Электрическая схема, предназначенная для выполнения какой-либо логической операции с входными данными, называется логическим элементом. Входные данные представляются здесь в виде напряжений различных уровней, и результат логической операции на выходе — также получается в виде напряжения определенного уровня.

Операнды в данном случае подаются в двоичной системе счисления — на вход логического элемента поступают сигналы в форме напряжения высокого или низкого уровня, которые и служат по сути входными данными. Так, напряжение высокого уровня — это логическая единица 1 — обозначает истинное значение операнда, а напряжение низкого уровня 0 — значение ложное. 1 — ИСТИНА, 0 — ЛОЖЬ.

Логический элемент — элемент, осуществляющий определенные логические зависимость между входными и выходными сигналами. Логические элементы обычно используются для построения логических схем вычислительных машин, дискретных схем автоматического контроля и управления. Для всех видов логических элементов, независимо от их физической природы, характерны дискретные значения входных и выходных сигналов.

Логические элементы имеют один или несколько входов и один или два (обычно инверсных друг другу) выхода. Значения «нулей» и «единиц» выходных сигналов логических элементов определяются логической функцией, которую выполняет элемент, и значениями «нулей» и «единиц» входных сигналов, играющих роль независимых переменных. Существуют элементарные логические функции, из которых можно составить любую сложную логическую функцию.

В зависимости от устройства схемы элемента, от ее электрических параметров, логические уровни (высокие и низкие уровни напряжения) входа и выхода имеют одинаковые значения для высокого и низкого (истинного и ложного) состояний.

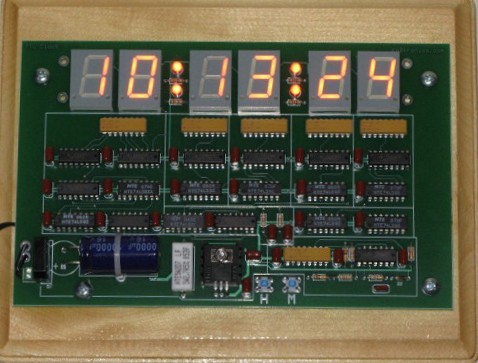

Традиционно логические элементы выпускаются в виде специальных радиодеталей — интегральных микросхем. Логические операции, такие как конъюнкция, дизъюнкция, отрицание и сложение по модулю (И, ИЛИ, НЕ, исключающее ИЛИ) — являются основными операциями, выполняемыми на логических элементах основных типов. Далее рассмотрим каждый из этих типов логических элементов более внимательно.

Логический элемент «И» — конъюнкция, логическое умножение, AND

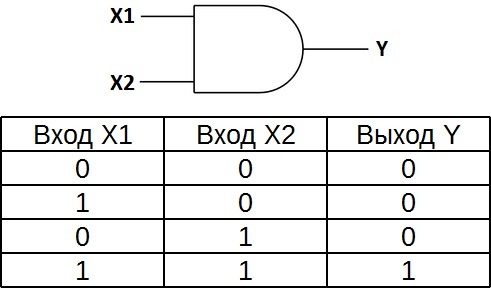

«И» — логический элемент, выполняющий над входными данными операцию конъюнкции или логического умножения. Данный элемент может иметь от 2 до 8 (наиболее распространены в производстве элементы «И» с 2, 3, 4 и 8 входами) входов и один выход.

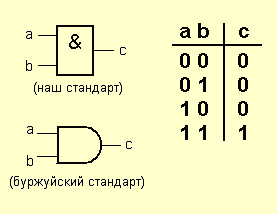

Условные обозначения логических элементов «И» с разным количеством входов приведены на рисунке. В тексте логический элемент «И» с тем или иным числом входов обозначается как «2И», «4И» и т. д. — элемент «И» с двумя входами, с четырьмя входами и т. д.

Таблица истинности для элемента 2И показывает, что на выходе элемента будет логическая единица лишь в том случае, если логические единицы будут одновременно на первом входе И на втором входе. В остальных трех возможных случаях на выходе будет ноль.

На западных схемах значок элемента «И» имеет прямую черту на входе и закругление на выходе. На отечественных схемах — прямоугольник с символом «&».

Логический элемент «ИЛИ» — дизъюнкция, логическое сложение, OR

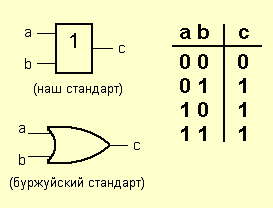

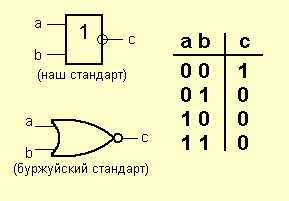

«ИЛИ» — логический элемент, выполняющий над входными данными операцию дизъюнкции или логического сложения. Он так же как и элемент «И» выпускается с двумя, тремя, четырьмя и т. д. входами и с одним выходом. Условные обозначения логических элементов «ИЛИ» с различным количеством входов показаны на рисунке. Обозначаются данные элементы так: 2ИЛИ, 3ИЛИ, 4ИЛИ и т. д.

Таблица истинности для элемента «2ИЛИ» показывает, что для появления на выходе логической единицы, достаточно чтобы логическая единица была на первом входе ИЛИ на втором входе. Если логические единицы будут сразу на двух входах, на выходе также будет единица.

На западных схемах значок элемента «ИЛИ» имеет закругление на входе и закругление с заострением на выходе. На отечественных схемах — прямоугольник с символом «1».

Логический элемент «НЕ» — отрицание, инвертор, NOT

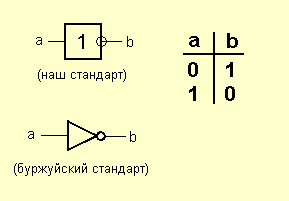

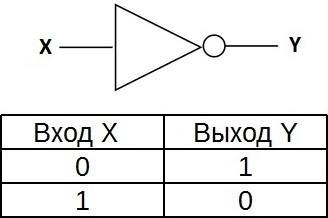

«НЕ» — логический элемент, выполняющий над входными данными операцию логического отрицания. Данный элемент, имеющий один выход и только один вход, называют еще инвертором, поскольку он на самом деле инвертирует (обращает) входной сигнал. На рисунке приведено условное обозначение логического элемента «НЕ».

Таблица истинности для инвертора показывает, что высокий потенциал на входе даёт низкий потенциал на выходе и наоборот.

На западных схемах значок элемента «НЕ» имеет форму треугольника с кружочком на выходе. На отечественных схемах — прямоугольник с символом «1», с кружком на выходе.

Логический элемент «И-НЕ» — конъюнкция (логическое умножение) с отрицанием, NAND

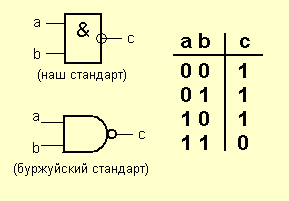

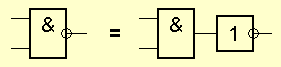

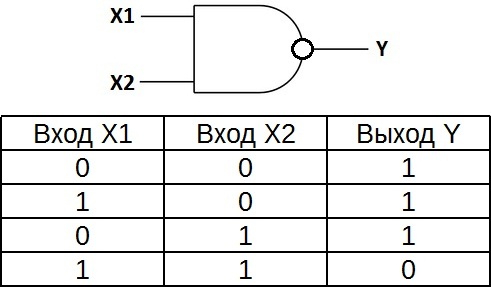

«И-НЕ» — логический элемент, выполняющий над входными данными операцию логического сложения, и затем операцию логического отрицания, результат подается на выход. Другими словами, это в принципе элемент «И», дополненный элементом «НЕ». На рисунке приведено условное обозначение логического элемента «2И-НЕ».

Таблица истинности для элемента «И-НЕ» противоположна таблице для элемента «И». Вместо трех нулей и единицы — три единицы и ноль. Элемент «И-НЕ» называют еще «элемент Шеффера» в честь математика Генри Мориса Шеффера, впервые отметившего значимость этой логической операции в 1913 году. Обозначается как «И», только с кружочком на выходе.

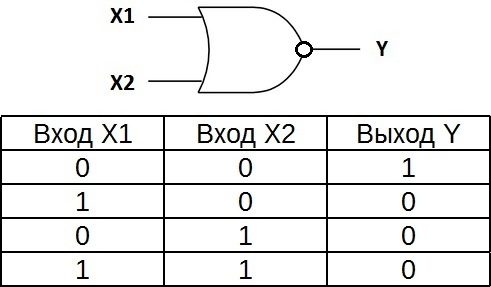

Логический элемент «ИЛИ-НЕ» — дизъюнкция (логическое сложение) с отрицанием, NOR

«ИЛИ-НЕ» — логический элемент, выполняющий над входными данными операцию логического сложения, и затем операцию логического отрицания, результат подается на выход. Иначе говоря, это элемент «ИЛИ», дополненный элементом «НЕ» — инвертором. На рисунке приведено условное обозначение логического элемента «2ИЛИ-НЕ».

Таблица истинности для элемента «ИЛИ-НЕ» противоположна таблице для элемента «ИЛИ». Высокий потенциал на выходе получается лишь в одном случае — на оба входа подаются одновременно низкие потенциалы. Обозначается как «ИЛИ», только с кружочком на выходе, обозначающим инверсию.

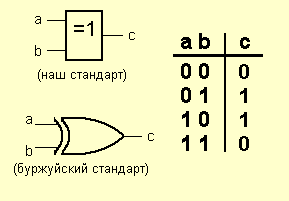

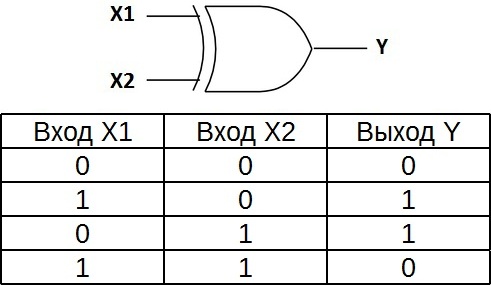

Логический элемент «исключающее ИЛИ» — сложение по модулю 2, XOR

«исключающее ИЛИ» — логический элемент, выполняющий над входными данными операцию логического сложения по модулю 2, имеет два входа и один выход. Часто данные элементы применяют в схемах контроля. На рисунке приведено условное обозначение данного элемента.

Изображение в западных схемах — как у «ИЛИ» с дополнительной изогнутой полоской на стороне входа, в отечественной — как «ИЛИ», только вместо «1» будет написано «=1».

Этот логический элемент еще называют «неравнозначность». Высокий уровень напряжения будет на выходе лишь тогда, когда сигналы на входе не равны (на одном единица, на другом ноль или на одном ноль, а на другом единица) если даже на входе будут одновременно две единицы, на выходе будет ноль — в этом отличие от «ИЛИ». Данные элементы логики широко применяются в сумматорах.

Цифровые интегральные схемы предназначены для обработки, преобразования и хранения цифровой информации. Они выпускаются сериями. Внутри каждой серии имеются объединенные по функциональному признаку группы устройств: логические элементы, триггеры, регистры, счетчики, дешифраторы, шифраторы, мультиплексоры, демультиплексоры и т.д. Чем шире функциональный состав серии, тем большими возможностями может обладать цифровое устройство, выполненное на базе микросхем данной серии. Микросхемы, входящие в состав каждой серии, имеют единое конструктивно-технологическое исполнение, одинаковое напряжение питания и одинаковые уровни сигналов логического нуля и логической единицы. Все это делает микросхемы одной серии совместимыми.

Основой каждой серии цифровых микросхем является базовый логический элемент. Как правило, базовые логические элементы выполняют операции И—НЕ, либо ИЛИ—НЕ и по принципу построения делятся на следующие основные типы: элементы резистивно-транзисторной логики (РТЛ), диодно-транзисторной логики (ДТЛ), транзисторно-транзисторной логики (ТТЛ), эмиттерно-связанной логики (ЭСЛ), интегрально-инжекционной логики (ИИЛ), базовые элементы которых выполнены на биполярных транзисторах. Микросхемы на комплементарных МДП-структурах (КМДП) используют пары МДП-транзисторов со структурой металл — диэлектрик – полупроводник с каналами р- и n-типов.

3.2.1 Схема ДТЛ ‑ диодно-транзисторной логики

Основная схема ДТЛ приведена на рисунке 3.9,а. Здесь диоды VD1, VD2, VD3 и резистор R1 представляют собой конъюнктор (И), элементы VT, R2, R3 – инвертор (НЕ). Смещающие диоды VDСМ1, VDСМ2 осуществляют связь между логическими элементами И и НЕ и смещают (понижают) потенциал базы VT относительно напряжения U1. Резистор R2 служит для подачи смещения ЕСМ на VT и гарантированного удерживания его в запертом состоянии при открытых входных диодах и как дополнительная цепь обратного тока базы при запирании транзистора.

Основная схема ДТЛ приведена на рисунке 3.9,а. Здесь диоды VD1, VD2, VD3 и резистор R1 представляют собой конъюнктор (И), элементы VT, R2, R3 – инвертор (НЕ). Смещающие диоды VDСМ1, VDСМ2 осуществляют связь между логическими элементами И и НЕ и смещают (понижают) потенциал базы VT относительно напряжения U1. Резистор R2 служит для подачи смещения ЕСМ на VT и гарантированного удерживания его в запертом состоянии при открытых входных диодах и как дополнительная цепь обратного тока базы при запирании транзистора.

При высоком уровне напряжения на входе UA = UB = UC = U 1 , диоды VD1…VD3 заперты, повышается потенциал точки U1, отпираются диоды смещения VDСМ1, VDСМ2, течет ток базы VT, и транзистор входит в насыщение. Напряжение на коллекторе UF падает до нуля, т.е. F = 0.

Если хотя бы на одном из входов низкий уровень напряжения UA или UB или UC равен U 0 , отпирается соответствующий диод, понижается потенциал U1, запираются диоды смещения VDCМ1, VDСМ2. На базе транзистора VT низкое напряжение, и он запирается. UВЫХ = UF = U 1 , т.е. на выходе элемента появляется логическая единица.

Если отбросить часть схемы (см. рисунок 3.9,а), изображенную пунктиром, она превращается в инвертор.

Если к схеме, в соответствии с рисунком 3.9,а, добавить диоды VD2, VD3, то напряжение UF будет соответствовать логической 1, если хотя бы один из входов будет в состоянии логического нуля. Логический нуль на выходе можно получить только в том случае, если на всех входах присутствует напряжение логической единицы, т.е. логическая операция, выполняемая данной схемой, имеет вид:  , что соответствует операции И-НЕ. Добавлением дополнительных диодов для расширения объема входа число входов в базовом элементе ДТЛ И-НЕ может быть доведено до 20.

, что соответствует операции И-НЕ. Добавлением дополнительных диодов для расширения объема входа число входов в базовом элементе ДТЛ И-НЕ может быть доведено до 20.

3.2.2 Схемы ТТЛ − транзисторно-транзисторной логики

3.2.2.1 Схема ТТЛ − транзисторно-транзисторной логики с простым инвертором

Транзисторно-транзисторная логика (см. рисунок 3.10) − результат развития ДТЛ. Матрица диодов заменяется многоэмиттерным транзистором (МЭТ).

Транзисторно-транзисторная логика (см. рисунок 3.10) − результат развития ДТЛ. Матрица диодов заменяется многоэмиттерным транзистором (МЭТ).

Это интегральный прибор, объединяющий функции диодных логических схем и транзисторного усилителя. МЭТ имеет несколько эмиттеров, расположенных так, что прямое взаимодействие между ними исключается. МЭТ позволяет увеличить быстродействие, снизить потребляемую мощность и усовершенствовать технологию изготовления микросхем. Так как МЭТ был разработан лишь на этапе интегральной схемотехники, то аналогов ТТЛ на дискретных компонентах не было.

ТТЛ относится к потенциальным элементам. При построении схем ЭВМ на их основе они соединяются потенциальными связями, т.е. без конденсаторов и трансформаторов.

Напряжение логической единицы – U 1 = 2,4 В, напряжение логического нуля – U 0

Базовый элемент ТТЛ так же, как и ДТЛ выполняет логическую операцию И-НЕ. При низком уровне сигнала (логический 0) хотя бы на одном из входов многоэмиттерного транзистора МЭТ последний находится в состоянии насыщения, а VT1 закрыт. На выходе схемы присутствует высокий уровень напряжения (логическая единица). При высоком уровне сигнала на всех входах МЭТ работает в активном инверсном режиме (эмиттерный переход смещен в обратном направлении, а коллекторный – в прямом), VT1 находится в состоянии насыщения. На выходе схемы низкий уровень сигнала, т.е. ноль.

Описанный здесь базовый элемент ТТЛ, несмотря на упрощенную технологию изготовления, не нашел широкого применения из-за низкой помехоустойчивости, малого быстродействия при работе на емкостную нагрузку и малой нагрузочной способности.

Низкая нагрузочная способность или малый коэффициент разветвления объясняется следующим образом. Через R2, при запертом транзисторе VT1, текут входные токи нагрузочных элементов, и, если их много, увеличивается падение напряжения на коллекторной нагрузке R2. Уменьшается напряжение на коллекторе VT1, т.е. значение верхнего логического уровня, нарушается работа схемы. Поэтому используется ТТЛ со сложным инвертором.

3.2.2.2 Схема ТТЛ со сложным инвертором

3.2.2.2 Схема ТТЛ со сложным инвертором

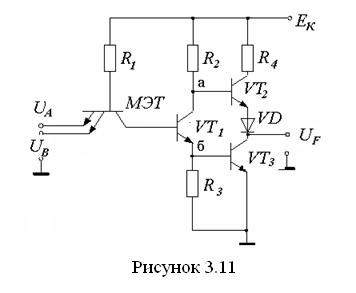

Схема ТТЛ (см. рисунок 3.11) состоит из двух частей:

а) конъюнктора И, включающего многоэмиттерный транзистор МЭТ и резистор R1. Схема И может иметь от 2 до 8 входов (увеличение количества входов расширяет логические возможности ТТЛ);

В свою очередь сложный инвертор можно рассматривать, состоящим из фазорасщепля-ющего каскада и выходного усилителя.

Фазорасщепляющий или фазоинверсный каскад (состоит из VT1, R2, R3) служит для управления транзисторами VТ2 и VТ3. Транзистор VТ1 увели-чивает порог переключения, повышает помехоустойчивость ТТЛ.

Выходной усилитель (VТ2, VТ3, VD, R4) представляет собой эмиттерный повторитель.

Транзисторы VТ1, VТ3 представляют составной транзистор или пару Дарлингтона. В статических режимах работы схемы VT3 повторяет состояние VT1. При запирании VT1база транзистора VT3 через резистор R3 подключается к корпусу, чем и обеспечивается закрытое состояние VT3.

Транзистор VТ2 может работать в насыщении и в отсечке. Его состояние в статических режимах работы схемы всегда противоположно состоянию VT3, следовательно, VT1. При насыщенном транзисторе VT3 транзистор VT2 закрыт и наоборот. Транзисторы VТ2, VТ3 представляют собой не что иное, как двухтактный усилитель мощности.

Диод VD служит для надежного запирания VТ2, когда открыт VТ3. Повышая порог отпирания VT2, он обеспечивает его закрытое состояние при насыщенном транзисторе VT3. Действительно:

где В – коэффициент передачи тока в режиме большого сигнала;

n – количество нагрузочных ТТЛ-схем, подключенных к выходу рассматриваемой схемы;

I 0 ВХ НАГР – входной ток нагрузочной ТТЛ-схемы.

Отсюда можно определить нагрузочную способность данной схемы, т.е. максимальное число нагрузочных схем, при котором транзистор VT3 еще работает в режиме насыщения:

Резистор R4 необходим для:

а) защиты VТ2 и VD в случае короткого замыкания на выходе;

б) ограничения коллекторного тока VТ2 при переключении схемы, из логического нуля в логическую единицу. После запирания VT1 транзистор VT2 откроется раньше, чем закроется насыщенный транзистор VT3, так как для выхода VT3 из режима насыщения потребуется некоторое время для рассасывания неосновных носителей в базе. В результате, в течение некоторого промежутка времени, оба транзистора VT2 и VT3 открыты, и по цепи, состоящей из элементов Ек, VT2, VD и VT3, протекает ток, потребляемый от источника питания Ек, и возникает импульс помехи по шине питания. Для ограничения амплитуды помехи ставится резистор R4, равный примерно нескольким десяткам омов.

Схема ТТЛ работает следующим образом. Если хотя бы на одном из входов низкий уровень напряжения U 0 ВХ эмиттерный переход МЭТ отпирается и течет ток: от +ЕК, через R1, переход база-эмиттер на землю. Коллекторный переход МЭТ смещен в обратном направлении (МЭТ в активном режиме). Ток базы IБ1 = 0, следовательно, транзистор VT1 запирается. На коллекторе VT1 высокий уровень напряжения UК1 = ЕК. На эмиттере VT1 напряжение UЭ1 = 0.

Если же на всех входах ТТЛ высокий уровень U 1 , эмиттерные переходы МЭТ запираются, потенциал базы увеличивается, коллекторный переход МЭТ смещается в прямом направлении. МЭТ работает в активно-инверсном режиме.

Транзисторы VТ1 и VТ3 открыты и насыщены. Транзистор VТ2 и диод VD заперты. На выходе ТТЛ низкий уровень UВЫХ = U 0 = 0. Следовательно, ТТЛ выполняет операцию И-НЕ, т.е. является элементом Шеффера.

Быстродействие схем ТТЛ определяется в основном переходными процессами при переключении транзисторов, а также зарядом паразитной суммарной емкости СН нагрузочных ТТЛ-схем. В схеме ТТЛ с простым инвертором (см. рисунок 3.10) заряд емкости СН происходит с большой постоянной времени через коллекторный резистор R2, что ухудшает быстродействие схемы.

В схеме ТТЛ со сложным инвертором постоянная заряда нагрузочной емкости существенно уменьшается, так как емкость СН заряжается через выходное сопротивление транзистора VT3 (Rвых 3

Не нашли то, что искали? Воспользуйтесь поиском:

Лучшие изречения: Учись учиться, не учась! 10458 —  | 7918 —

| 7918 —  или читать все.

или читать все.

|

|

|

|

|

|

Поскольку вам придется общаться как с русской, так и с буржуйской тех. документацией, я буду приводить условные графические обозначения (УГО) элементов и по нашим и по не нашим стандартам. Смотрим таблицу истинности, и проясняем в мозгу принцип. Понять его не сложно: единица на выходе элемента «И» возникает только тогда, когда на оба входа поданы единицы. Это объясняет название элемента: единицы должны быть И на одном, И на другом входе. Если посмотреть чуток иначе, то можно сказать так: на выходе элемента «И» будет ноль в том случае, если хотя бы на один из его входов подан ноль. Запоминаем. Идем дальше. По другому, его зовут «дизъюнктор».

Опять же, название говорит само за себя. На выходе возникает единица, когда на один ИЛИ на другой ИЛИ на оба сразу входа подана единица. Этот элемент можно назвать также элементом «И» для негативной логики: ноль на его выходе бывает только в том случае, если и на один и на второй вход поданы нули. Едем дальше. Дальше у нас очень простенький, но очень необходимый элемент. Чаще, его называют «инвертор».

Надо чего-нибудь говорить по поводу его работы? Ну тогда поехали дальше. Следующие два элемента получаются путем установки инвертора на выход элементов «И» и «ИЛИ». Элемент «И-НЕ» (NAND)

Элемент И-НЕ работает точно так же как «И», только выходной сигнал полностью противоположен. Там где у элемента «И» на выходе должен быть «0», у элемента «И-НЕ» — единица. И наоборот. Э то легко понять по эквивалентной схеме элемента:

Элемент «ИЛИ-НЕ» (NOR)

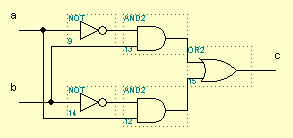

Та же история – элемент «ИЛИ» с инвертором на выходе. Следующий товарищ устроен несколько хитрее: Элемент «Исключающее ИЛИ» (XOR)

Операция, которую он выполняет, часто называют «сложение по модулю 2». На самом деле, на этих элементах строятся цифровые сумматоры. Смотрим таблицу истинности. Когда на выходе единицы? Правильно: когда на входах разные сигналы. На одном – 1, на другом – 0. Вот такой он хитрый. Эквивалентная схема примерно такая:

Ее запоминать не обязательно. Собственно, это и есть основные логические элементы. На их основе строятся абсолютно любые цифровые микросхемы. Даже ваш любимый Пентиум 4. Далее мы позанудствуем о том, как синтезировать цифровую схему, имея ее таблицу истинности. Это совсем несложно, а знать надо, ибо пригодится (еще как пригодится) нам в дальнейшем. Ну и напоследок – несколько микросхем, внутри которых содержатся цифровые элементы. Около выводов элементов обозначены номера соответствующих ног микросхемы. Все микросхемы, перечисленные здесь, имеют 14 ног. Питание подается на ножки 7 (-) и 14 (+). Напряжение питания – смотри в таблице в предыдущем параграфе. «> |