Нагрузочная способность — логический элемент

Нагрузочная способность логического элемента п определяет количество входов идентичных элементов, на которые может быть нагружен выход данного элемента, при неискаженной передаче двоичных символов. Иногда нагрузочная способность называется коэффициентом разветвления по выходу. [2]

Нагрузочная способность логического элемента зависит от допустимых колебаний напряжения питания, нап ряжений входных сигналов и изменений температуры окружающей среды. Расчет логических элементов производится, как правило, для наихудших режимов и условий работы. [4]

Нагрузочная способность логического элемента определяет его коэффициент разветвления N. [5]

Нагрузочную способность логических элементов на микросхемах И2Л следует определять с учетом неравномерного распределения базовых токов между инверторами, входы которых подключены к общему выходу. [7]

В промышленности для повышения нагрузочной способности логических элементов ДТЛ и ТТЛ используют схемы со сложным инвертором. Инвертирование фазы сигнала осуществляется сложным инвертором на транзисторах Т2, Т3, Т, питание элемента — источником постоянного напряжения Ек 5 В. [8]

Коэффициент разветвления по выходу характеризует нагрузочную способность логического элемента и определяется количеством входов однотипных элементов, которые можно подключить к выходу. В некоторых случаях в ТУ указывается максимальный выходной ток логического элемента. [9]

В контактных схемах эта функция используется для размножения числа контактов реле, а в бесконтактных необходима для увеличения нагрузочной способности логических элементов . Кроме того, повторители используются для согласования некоторых элементов, которые непосредственно соединять нельзя. [11]

Расчет для наихудших условий приводит к увеличению надежности конкретной схемы, но сильно ограничивает максимальное число входов и нагрузочную способность логических элементов . [12]

Так как вероятность того, что величины всех компонентов имеют одновременно отклонения в худшую сторону, мала, то для повышения числа входов и нагрузочной способности логических элементов можно использовать метод статистического расчета. В результате достигается уменьшение числа элементов, что может увеличить надежность всего устройства в целом. Для многих применений можно использовать специальный случай статистического расчета, когда значения сопротивлений и напряжений источников питания приняты номинальными, а значения коэффициента усиления транзистора и токов утечки наихудшими. Такой расчет схем обычно дает достаточно высокую точность. [13]

Усложнение схемы в этом случае направлено на устранение эффекта динамического запирания транзисторов выходных эмиттерных повторителей при работе на большую емкостную нагрузку и тем самым увеличивает динамическую нагрузочную способность логического элемента . [14]

Нагрузочная способность логических элементов в значительной степени определяется характеристиками инвертора. [15]

Логические, схемотехнические и эксплуатационные свойства логических элементов определяются совокупностью характеристик и параметров, к которым относят:

· функции логических элементов;

· коэффициенты объединения по входу и выходу;

· входные и выходные напряжения и токи;

· статическая и динамическая помехоустойчивость;

· допустимые величины механических воздействий, диапазоны давления и температуры окружающей среды, устойчивость к радиационным воздействиям;

· масса, стоимость и конструктивное оформление.

В большинстве случаев указанные характеристики и параметры относятся и к ИМС, на которых реализованы логические элементы.

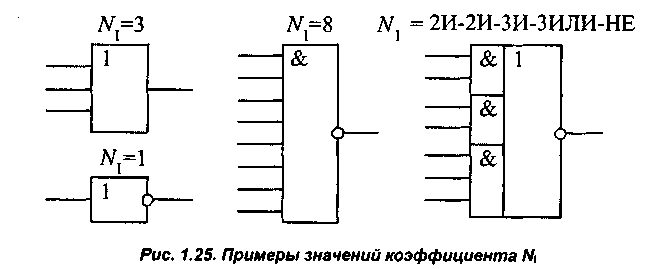

Коэффициент объединения по входу NI характеризует число логических входов логического элемента — обычно 1, 2, 3, 4 или 8 (рис.4.6).

Рисунок 4.6-Примеры значений коэффициента NI

Коэффициент объединения по выходу N0 характеризует допустимое количество соединенных между собою выходов логических элементов с целью создания новых функций.

Коэффициент разветвления по выходу Np характеризует нагрузочную способность логического элемента, то есть максимальное число входов идентичных схем, которое может быть одновременно подключено к выходу данного элемента без нарушения его работоспособности (рис. 4.7).

В состав серий ИМС обычно входят элементы с малой нагрузочной способностью (Nр = 3. 15) и с большой (Np = 30. 50).

Рисунок 4.7-Подключение нагрузки: а)- Np=3 б) Np=4

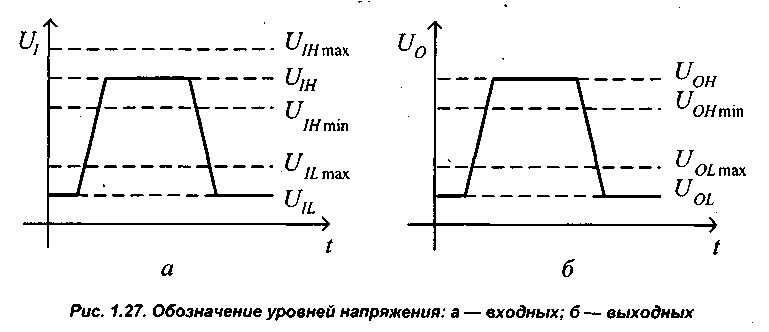

Приняты следующие определения и буквенные обозначения электрических параметров цифровых микросхем (ДСТУ 2883-94):

• входные UI, и выходные UO уровни напряжений (индексы — от английских слов Input и Output);

• входные напряжения низкого UIL и высокого UIH уровней; для них устанавливаются максимальное значение низкого уровня UIL max и минимальное значение высокого уровня UIHmin (рис. 4.8);

• выходные напряжения низкого U0l и высокого Uoh уровней; для них установлены максимальное значение низкого уровня U0lmax и минимальное значение высокого уровня UIHmin;

• входной I1 и выходной I0 токи;

• входной ток IIL — при низком уровне напряжения на входе, I1H — при высоком;

• выходной ток IOL — при низкому уровне напряжения на входе, а I0H — при высоком;

• Ucc — значение напряжения источника питания;

• Icc — ток, потребляемый ИМС от источника питания;

• Рсс — мощность, потребляемая ИМС от источника питания;

• входные пороговые напряжения, при которых происходит переключение элемента: UTIH — наименьшее значение для высокого уровня и UTIL — наибольшее значение для низкого уровня.

Рисунок 4.8-Обозначение уровней напряжения

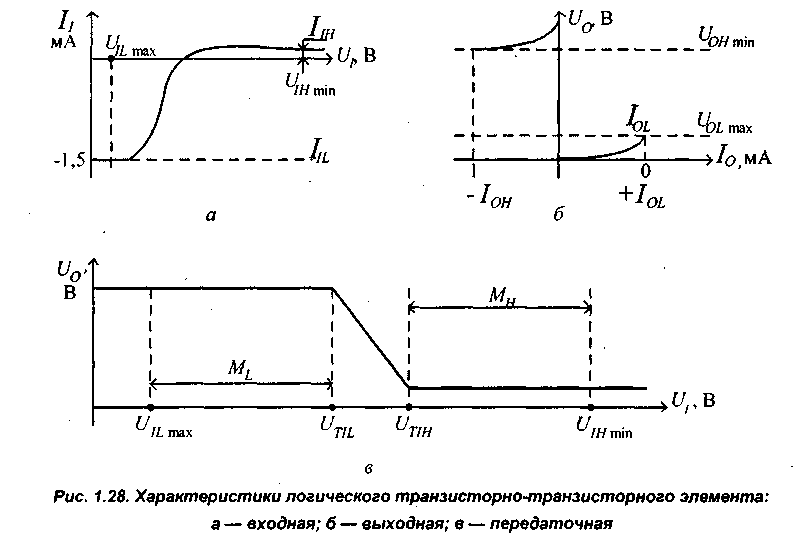

Основные параметры логических элементов определяют с помощью входной, выходной и передаточной характеристик. Типовые графики этих характеристик для инвертирующих элементов транзисторно-транзисторной логики представлены на рис. 4.9.

Входная характеристика логического элемента II = f(UI) — это зависимость входного тока от изменения входного напряжения.

Токи, втекающие в схему элемента, считаются положительными, а вытекающие — отрицательными (рис.4.9,а).

Из этой характеристики определяют входные токи IIL для напряжения UIL max и токи IIH для напряжения UIHmin.

Выходная характеристика логического элемента UO = f(Io) определяет зависимость выходного напряжения от тока нагрузки для состояний высокого и низкого уровней (рис. 4.9, б). Из этой характеристики определяют допустимые значения токов: +I0L — при низком уровне выходного напряжения UOL max и -I0Н — при высоком уровне напряжения UOHmin (рис. 4.9, б).

Рисунок 4.9-Характеристики логического ТТЛ-элемента:

а)-входная, б)-выходная, в)-передаточная

Передаточная характеристика U0 – f(UI) — это зависимость выходного напряжения от входного (рис. 4.9, в).

Из этой характеристики определяют значение помехоустойчивостидля низкого уровня на входе ML (отпирающая помеха) и для высокого уровня на входе МH (запирающая помеха):

Средняя мощность Р*CC. потребляемая элементом от источника питания вычисляется по формуле

где ICCL и Icch — токи потребления при низком и высоком уровнях напряжения на выходе соответственно;

I*cc — средний ток потребления.

Современные элементы потребляют мощность от микроватт до десятков милливатт.

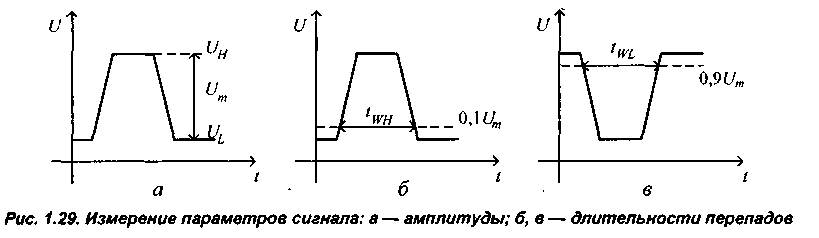

Потенциальные сигналы характеризуются значением логического перепада (амплитудой) Um = UH — UL и длительностью положительного tWH и отрицательного tWL перепадов (рис. 4.10).

Перепады напряжений часто называют положительными и отрицательными импульсами.

Рисунок 4.10-Измерение параметров сигнала:

а)-амплитуды, б, в)-длительности перепада

Для измерения временных параметров сигнала устанавливают условные уровни в долях амплитуды — 0,1; 0,5 и 0,9.

Быстродействие микросхем определяют по значениям следующих длительностей:

• фронта tLH и спада tHL (рис. 4.11, а);

• собственно включения tTHL и выключения tTLH (рис.4.11,б); и их задержки соответственно tDHL и tDLH;

• задержек распространения сигнала при включении tPHL и выключении tPLH (рис.4.11,в).

Рисунок 4.11- Измерение временных параметров сигналов:

а)-фронта и спада, б)-времени включения и выключения, в)—времени задержек распространения сигнала при включении tPHL и выключении tTLH

Надежность ИМС характеризуется тремя взаимозависимыми показателями:

• интенсивностью отказов  = n/ (mt),

= n/ (mt),

где n — число отказов за время испытания, час;

m — общее количество испытуемых микросхем;

• наработкой на отказ Т = 1/

• возможностью безотказной работы на протяжении заданного интервала времени

Р = ехр(-  ).

).

Для современных ИМС интенсивность отказов  = (10 -7 . 10 -8 ). Приняв, что

= (10 -7 . 10 -8 ). Приняв, что  = 10 -8 , t = 15000, получим значение вероятности безотказной работы P(t) = 0,998 или 99,8%.

= 10 -8 , t = 15000, получим значение вероятности безотказной работы P(t) = 0,998 или 99,8%.

По конструктивно-технологическому исполнению микросхемы подразделяются на пять групп, которым присвоены следующие обозначения (ДСТУ 3212-95):

• полупроводниковым на биполярных транзисторах — 1, 6;

• полупроводниковым на полевых транзисторах — 5, 7;

• другим (пленочным, вакуумным, керамическим и т.д.) — 3;

• резервным — 0, 8, 9.

По функциональному назначению микросхемы подразделяются на группы, которым присваиваются следующие обозначения:

• коммутаторы и ключи — К;

• логические элементы — Л;

• многофункциональные схемы — X;

• наборы элементов — Н;

• преобразователи сигналов — П;

• схемы источников вторичного электропитания — Е;

• схемы задержки — Б;

• схемы сравнения — С;

• схемы запоминающих устройств — Р;

• схемы цифровых устройств — И;

• схемы вычислительных средств — В.

В каждой функциональной группе различают виды, например:

ЛЛ — элемент ИЛИ;

ЛА — элемент НЕ-И;

ЛЕ — элемент НЕ-ИЛИ;

ЛР — элемент НЕ-И-ИЛИ;

ТВ — универсальные (тип JK);

ТР — с раздельной записью (тип RS);

ТМ — с задержкой (тип D);

• схем вычислительных средств:

ВС — микропроцессорные секции;

ВУ — схемы микропрограммного управления;

ВБ — схемы синхронизации;

ВВ — схемы интерфейса;

ВН — времязадающие схемы;

Для характеристики материала и типа корпуса по ГОСТ 174-67 перед цифровым обозначением серии добавляются следующие буквы;

Р — для пластмассового корпуса типа 2;

М — для керамического, металлокерамического корпуса типа 2;

Е — для металлополимерного корпуса типа 2;

С — для стеклокерамического корпуса типа 2 и др.

Для некоторых микросхем буквенные обозначения типа корпуса не применяют.

Присвоение обозначений микросхемам осуществляет в Централизованном порядке главная организация по стандартизации изделий электронной техники.

Обозначение микросхемы должно состоять из следующих элементов:

• первый и второй элементы — две цифры, характеризующие соответственно группу и подгруппу микросхемы по конструктивно-технологическому исполнению;

• третий элемент — две цифры, обозначающие порядковый номер разработки серии микросхем;

• четвертый элемент — две буквы, характеризующие соответственно группу и вид микросхемы;

• пятый элемент — две цифры, обозначающие порядковый номер разработки микросхемы.

Три первых элемента определяют серию микросхем. В случае необходимости после обозначения порядкового номера разработки микросхемы по функциональному назначению дополнительно проставляются буквы от А до Я, характеризующие отличие микросхем одного типа по электрическим параметрам. Такая буква во время маркировки может быть заменена цветной точкой. Буква или цвет маркировочной точки указываются в технических условиях микросхем конкретных типов.

Примеры условного обозначения микросхем:

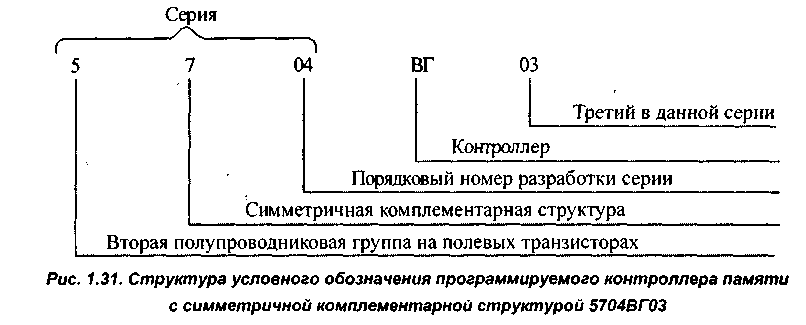

• 5704ВГ03 — полупроводниковый программируемый контроллер управления

динамической памятью с симметричной комплементарной структурой серии

5704; номер разработки серии — 04, номер разработки микросхемы в данной серии по функциональному назначению — 03 (рис. 1.31);

• 1101УД06 — полупроводниковая микросхема серии 1101, порядковый номер разработки серии — 01, структура на биполярных транзисторах с изоляцией р-п переходом, операционный усилитель постоянного тока, порядковый номер разработки микросхемы в данной серии по функциональному назначению — 06.

Рисунок 4.12- Структура условного обозначения микросхемы 5704ВГ03

Перед условным обозначением микросхем указывается сокращенное название государства-разработчика — У (Украина).

Для микросхем с шагом 1,27 или 2,54 мм между выводами корпуса, которые поставляются на экспорт, вначале условного обозначения после буквы У проставляется буква Е, например:

• УЕ1217УД06 — микросхемы серии 1217, выпущенные в Украине в экспортном исполнении (шаг выводов 1,27 или 2,54 мм) в пластмассовом корпусе типа 2. В ранее принятых обозначениях ИМС широкого применения вначале ставили букву К.

Не нашли то, что искали? Воспользуйтесь поиском:

Лучшие изречения: Для студентов недели бывают четные, нечетные и зачетные. 9496 —  | 7460 —

| 7460 —  или читать все.

или читать все.

91.146.8.87 © studopedia.ru Не является автором материалов, которые размещены. Но предоставляет возможность бесплатного использования. Есть нарушение авторского права? Напишите нам | Обратная связь.

Отключите adBlock!

и обновите страницу (F5)

очень нужно

К основным параметрам логических элементов относятся напряжение источника питания, уровни напряжений логического 0 и логической 1, нагрузочная способность, помехоустойчивость и быстродействие, потребляемая мощность.

Уровни лог. 0 и лог. 1 на входе и на выходе микросхем отличаются, как правило, до 30 % от напряжения источника питания. Кроме того, логические уровни КМОП микросхем существенно отличаются от логических уровней ТТЛ микросхем (см. рис. 3.8). Так при отсутствии тока нагрузки напряжение на выходе КМОП микросхемы совпадает с напряжением питания (уровень лог. 1) или с потенциалом общего провода (уровень лог. 0). При увеличении тока нагрузки напряжение лог. 1 может уменьшаться до 90 %, а напряжения лог. 0 – увеличиваться до 10 % от напряжения питания. На входе же КМОП микросхемы минимально допустимый уровень лог. 1 составляет 70 %, а лог. 0 – 30 % от напряжения питания.

У микросхем ТТЛ уровень лог. 1 находится в пределах от 40 % от напряжения питания (на входе) до 50 % на выходе. Уровень лог. 0 соответственно от 15 % (на входе) до 8 % на выходе.

У микросхем ТТЛ уровень лог. 1 находится в пределах от 40 % от напряжения питания (на входе) до 50 % на выходе. Уровень лог. 0 соответственно от 15 % (на входе) до 8 % на выходе.

Нагрузочная способность – способность элемента работать на определенное число входов других элементов без дополнительных устройств согласования характеризуется так называемым коэффициентом разветвления и оценивается числом единичных нагрузок, которые можно одновременно подключить к выходу микросхемы. Коэффициент разветвления по выходу для большинства логических элементов серий ТТЛ серии составляет 10, а для микросхем серий КМОП – до 100.

Следует отметить, что при повышении нагрузочной способности другие параметры микросхем ухудшаются: снижаются быстродействие и помехоустойчивость, возрастает потребляемая мощность.

Помехоустойчивость базовых логических элементов оценивают в статическом и динамическом режимах. При этом статическая помехоустойчивость определяется уровнем напряжения, подаваемого на вход элемента относительно уровней логических 0 и 1, при котором состояние на выходе схемы не изменяется. Для элементов ТТЛ статическая помехоустойчивость составляет не менее 0,4 В, а для микросхем серий КМОП – не менее 30 % напряжения питания.

Динамическая помехоустойчивость зависит от формы и амплитуды сигнала помехи, а также от скорости переключения логического элемента и его статической помехоустойчивости. Динамические параметры базовых элементов оценивают, в первую очередь, быстродействием. Количественно быстродействие можно характеризовать предельной рабочей частотой, т. е. максимальной частотой переключения. Предельная рабочая частота современных микросхем ТТЛ составляет свыше 10 МГц, а микросхем на КМОП структурах лишь 1 МГц.

Предельная частота ограничивается средним временем задержки распространения сигнала (см. рис. 3.9)

. (3.1)

. (3.1)

Для микросхем ТТЛ это время составляет около 20 нс, а для микросхем КМОП – около 200 нс.

Для микросхем ТТЛ это время составляет около 20 нс, а для микросхем КМОП – около 200 нс.

Потребляемая микросхемой мощность в статическом режиме оказывается различной при уровнях лог. 0 (Рлог.0) и лог. 1 (Рлог.1) на выходе. В связи с этим измеряют среднюю мощность потребления

. (3.2)

. (3.2)

Статическая средняя мощность потребления базовых элементов ТТЛ составляет несколько десятков милливатт, а у элементов КМОП она более чем в тысячу раз меньше.

Следует отметить, что при работе в динамическом режиме мощность, потребляемая логическими элементами, возрастает. Поэтому помимо потребляемой мощности в статическом режиме РСР микросхемы характеризуются также потребляемой мощностью в динамическом режиме РДИН, измеряемой на максимальной частоте переключений.

Контрольные вопросы и задания

1. Какие технологии построения логических элементов Вы знаете?

2. Нарисуйте и объясните принцип действия базового элемента диодно-транзисторной логика. Укажите недостатки по причине которых диодно-транзисторной логика не находит широкого применения.

3. Нарисуйте и объясните принцип действия базового элемента И-НЕ транзисторно-транзисторной логики.

4. Нарисуйте и объясните принцип действия базового элемента ИЛИ-НЕ эмиттерно-связанной транзисторной логики. Какими преимуществами ЭСЛ обладает перед ТТЛ?

5. Нарисуйте логические схемы и поясните работу элементов И-НЕ и ИЛИ-НЕ, реализованных на КМОП структурах.

6. Какие особенности применения КМОП микросхем Вы знаете?

7. Перечислите основные параметры логических элементов и поясните их.

Дата добавления: 2015-05-05 ; просмотров: 1502 ; ЗАКАЗАТЬ НАПИСАНИЕ РАБОТЫ